IJEMD-Engr, 1 (1) (2023), 1-6

https://doi.org/10.54938/ijemd-engr.v1i1.7

International Journal of Emerging Multidisciplinaries: Engineering

> Research Paper Journal Homepage: <u>www.ojs.ijemd.com</u> ISSN (print): 2957-5885

# Design specification and simulations of a Miller compensated Operational Amplifier with 75dB Gain

Muhammad Ahmad<sup>1\*</sup>, Sohail Ahmed<sup>1</sup>, Arshad Hussain<sup>1</sup> and Zeeshan Akbar<sup>1</sup>

<sup>1</sup> Department of Electronics, Faculty of Natural science, Quaid-i-Azam University, Islamabad, Pakistan \*Corresponding author

#### Abstract

This paper presents a two-stage Miller compensated operational amplifier design using cadence 55nm CMOS technology. This circuit provides a single ended output due to mirror pole is implemented while the input of this operational amplifier is differential. A biasing circuit is also designed and attached with this amplifier. This operational amplifier provides a gain of 75.41dB while the phase margin is off 70°. The Gain bandwidth of this operational amplifier is 9.5MHz. The power consumption of this overall circuit including the biasing circuit is 154.69 $\mu$ W. The other performance parameters are also analyzed and provide in this paper. The mathematical calculation for the circuits is also presented. Due to medium power consumption and higher gain bandwidth this amplifier can be used in different data converters like Delta-Sigma ADC. Because the performance of this ADC is depending upon the higher Gain Bandwidth.

Keywords: Gain bandwidth; Miller compensated; Mirror pole; Operational Amplifier; Slew-rate.

## 1. Introduction

An amplifier is an important building block for Data converters. The performance of the Delta sigma ADC depends upon the specifications of the operational amplifier. The Gain bandwidth, the open loop Gain of operational amplifier, phase margin and slew rate are the performance parameters of the operational amplifier. In this paper [3] a miller compensated two stage operational amplifier is designed using TSMC 0.18µm CMOS technology. This amplifier is designed to attain the requirements of delta sigma analog to digital converters like high resolution and high speed. But the disadvantage of this design is the power consumption which is 16.5mW. So, this design is not so good for low power applications. In another design [4] a miller compensated two stage operational amplifier is designed to meet the specifications. This design consists of an NMOS amplifier along with active load as first stage which is followed by PMOS amplifier

at second stage which attain a pole splitting and hence the operational amplifier compensation. This design is also a single ended output design, and the biasing circuit is attached. The power consumption of this operational amplifier is also greater which is not so good for data converter applications. A critical review of two stage miller compensation operational amplifier is proposed in this paper [5]. The trade of is also considered which is involved in small signal parameters and compensation capacitor value, as the second stage need a more biasing current it is working with a large load capacitor to attain phase margin. A method is presented to increase the transconductance without increasing the power consumption at second stage. A 65nm CMOS technology is used to perform the simulations with supply voltage of 1 volt.

### **Circuit Diagram:**

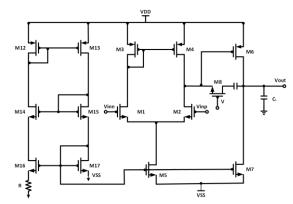

Figure 1: Schematic diagram of Op-Amp with biasing circuit

A miller compensated two stage operational amplifier is shown in the figure1. This circuit include a twostage operational amplifier and stable transconductance biasing circuit. The gain which is attain from 1<sup>st</sup> stage is usually high while due to common source technique the gain at second stage is moderate. As there is biasing circuit include so there is no need to provide biasing from other source. The input of the operational amplifier is differential while the output is single ended. The transistor M8 in the circuit is used as a resistor and we provide supply voltage to its input.

## **Design Calculations:**

In this section we will determine the equations for the calculations of aspect ratios of transistor using the basic operational amplifier equations.

From MOSFET, strong inversion, square law equations: According to this equation drain current  $(I_D)$

$$I_{\rm D} = \frac{1}{2} \beta V_{\rm ov}^2$$

Where the value of  $\beta$  is dependent upon the oxide capacitance and aspect ratio of the transistor.

$$B = \mu_n C_{ox}(\frac{W}{L})$$

The transconductance of the amplifier is

$$g_m = \frac{2*ID}{Vov}$$

For NMOS  $V_{ov} = (V_{gs} - V_{tn})$  and for PMOS  $V_{ov} = (V_{SG} - |V_{tp}|)$

Compensation capacitor is design in such a way that pole  $P_2$  is 2.2 time more than the GBW which will provide a  $60^0$  of phase margin. Now the next phase is to design the estimated biasing current. As we know

Slew rate (SR) =  $I_{ss}/C_c$ .

Where  $Iss = I_5$  which is the tail current. By using this equation, we can find tail current.

Now we assume that gain bandwidth is established by dominant node, so

$G_{m1} = GBW * C_c$  And

$(W/L)_{1,2} = (gm_1)^2/k_n * I_5$

From here we can find the aspect ratio of the transistor 1 and 2 For the aspect ratio of transistor 3 and 4

$$(W/L)_{3,4} = \frac{15}{15}$$

$(W/L)_{3,4} = \frac{1}{kp*[Vdd-Vin(max)-|Vtp,3|(max)+Vtn,1(min)]_2}$

Design for aspect ratio of transistor 5 from minimum input voltage.

$$V_{DS5} = V_{in}(min) - V_{SS} - \sqrt{\frac{I_1}{R_2}} - V_{tn,1}(max)$$

After calculating this we can find the aspect ratio is it depends upon the value of  $V_{DS5}$ .Now

$$\left(\frac{w}{l}\right)5 = \frac{2I_5}{k_{nC_{OX}}*(V_{DS5\,)2}}$$

Now finally the aspect ratio of 6 transistor can be calculated by finding the transconductance of transistor 4 and 6.

$$g_{m6} = 10^* g_{m1}$$

Now

$$\left(\frac{w}{l}\right)6 = \left(\frac{w}{l}\right)4 * \frac{g_{m6}}{g_{m4}}$$

$$\left(\frac{w}{l}\right)7 = \left(\frac{w}{l}\right)5 * \frac{I_6}{I_5}$$

$$\left(\frac{w}{l}\right)8 = \frac{\left(\frac{w}{l}\right)6}{1 + \frac{C_l}{C_r}}$$

By putting the values of our specifications, we can calculate the aspect ratios of all transistors from these above equations. And then put these values in circuit and then we have to optimize these ratios.

#### **Design Equations of bias Circuits:**

Current mirror M12,M13 causes M17 to conduct a current equal to that in M16. i.e I<sub>B</sub>.

$I_{B} = \frac{1}{2} \mu_{n} C_{ox} (\frac{W}{L})_{16,17} (V_{GS16,17} - V_{T})^{2}$ Applying K.V.L on V<sub>GS</sub> of M<sub>16</sub> and M<sub>17</sub> -V<sub>GS17</sub>+V<sub>GS16</sub>+I<sub>B</sub>R<sub>B</sub>=0

V<sub>GS17</sub>=V<sub>GS16</sub>+I<sub>B</sub>R<sub>B</sub>

Subtracting Vt from both sides  $(V_{GS17}-Vt) = (V_{GS16}-Vt) + I_BR_B$

$$I_{B} = \frac{2}{\mu_{n} Cox(\frac{W}{L})_{16} R_{B}^{2}} \left( \sqrt{\frac{(\frac{W}{L})_{16}}{(\frac{W}{L})_{17}}} - 1 \right)^{2}$$

$$I_{B} \propto \frac{1}{R_{B}^{2}}$$

$$R_{B} = \frac{2}{g_{m16}} \left( \sqrt{\frac{(\frac{W}{L})_{16}}{(\frac{W}{L})_{17}}} - 1 \right)$$

Here,  $g_{m16} = \sqrt{\mu_{n} Cox(\frac{W}{L})_{16}} I_{B}$

In order to generate  $18\mu$  of biasing current we use  $0.52K\Omega$  resistance.

#### Simulation

A miller compensated two stage operational amplifier is designed in 55nm CMOS technology. The first stage of the amplifier gives the high gain while the second stage provide moderate gain. The biasing circuit is also designed and attached to the operational amplifier instead of providing the DC voltage source. The Op-Amp has differential input and single ended output. The Load capacitance of capacitor is 100fF.

$C_c = 200 \text{fF}$  and  $C_L = 100 \text{fF}$

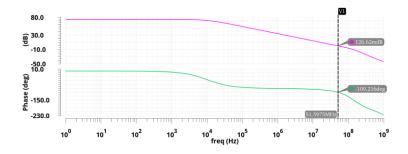

After performing the simulations, we attain a performance parameters like gain and phase of Op-Amp which is 75.41dB and 70° respectively. The plot of the gain and phase shown in the figure 2.

Figure 2: Gain and Phase plot

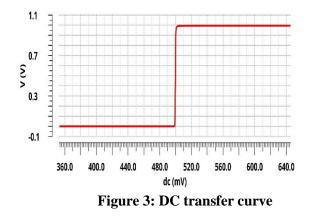

The offset voltage of this operational amplifier is <1mV which is attain from DC transfer curve. The open loop DC gain of the operational amplifier is 4870V/V. we also can calculate the input offset voltage by the formula given below.

Input offset voltage =  $\frac{output offset voltage}{Open loop DC gain}$

The unity gain frequency of this circuit is 51.6MHz while the gain Bandwidth product is 9.5MHz.

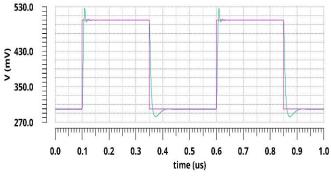

The step response of this operational amplifier is shown in the figure 4. We can find the slew rate of the operational amplifier from this plot whose value is 33 V/ $\mu$ s. All the performance calculations are shown in the table below.

Figure 4: step response of Op-Amp

| Table 1: Performance  |          |

|-----------------------|----------|

| Parameters            | Values   |

| Open loop gain        | 75.41dB  |

| Phase margin          | 70°      |

| Gain bandwidth        | 9.5MHz   |

| Output offset voltage | <1mV     |

| Unity Gain Frequency  | 51.6MHz  |

| DC gain               | 4870 V/V |

| Slew Rate             | 33 V/µs  |

| Power consumption     | 154.69µW |

#### 2. Conclusion

A two-stage miller compensation operational amplifier is designed in cadence 55nm CMOS technology for different types of data converters. The schematic diagram of the circuit is presented in the figure. The operational amplifier attains a gain of 75.41dB with the phase margin of 70°. The gain bandwidth of the operational amplifier is 9.5MHz while the other performance parameters are also calculated. The power consumption of the operational amplifier is 154.69µW while the supply voltage of 1 Volt.

## 3. References

[1] Allen, P. E. & Holberg, D. R., CMOS Analog Circuit Design, 2nd Ed., Oxford Unv. Press, 2002.

[2] Baker, R. J., Li, H. W. & Boyce, D. E. CMOS-Circuit Design, Layout, and Simulation, 3rd Ed., IEEE Press, 2013.

[3] Prema Kumar, G. & Kudikala, S. 2015, Design of Miller Compensated Two-Stage Operational Amplifier for Data Converter Applications, *International Journal of Engineering Research & Technology* (*IJERT*) **4**(5) (May 2015).

[4] Gomez, R. Design of Two-Stage Operational Amplifier using Indirect Feedback Frequency Compensation. Electrical Engineering Undergraduate Honors Theses, 2019.

[5] Nagulapalli, R., Hayatleh, K., Barker, S., Reddy, B. N. K. & Seetharamulu, B. "A Low Power Miller Compensation Technique for Two Stage Op-amp in 65nm CMOS Technology," *2019 10th International Conference on Computing, Communication and Networking Technologies (ICCCNT)*, 1-5 (2019).

[6] Awan, Javed, A. & Wilson, P. "Low power high speed operational amplifier design using cadence."[7] Baker, R. Jacob, "CMOS: Circuit Design, Layout, and Simulation" (2010).

[8] Mohammadpour, M. & Rostampour, M. "Indirect Miller effect based compensation in Low power two-stage operational Amplifiers," *2012 International Conference on Multimedia Computing and Systems*, Tangiers, Morocco, 1113-1116, doi: 10.1109/ICMCS.2012.6320278 (2012).

[9] Shanchana, S. et al. "Systematic Design and Analysis of Split Length Compensated Op-Amp Using gm/ID Technique," 2018 International Conference on Communication and Signal Processing (ICCSP), Chennai, India, 263-268 (2018).

[10] Sarma, M. P., Kalita, N. & Mastorakis, N. E. "Design of an low power miller compensated two stage OP-AMP using 45 nm technology for high data rate communication," 2017 4th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 463-467 (2017).